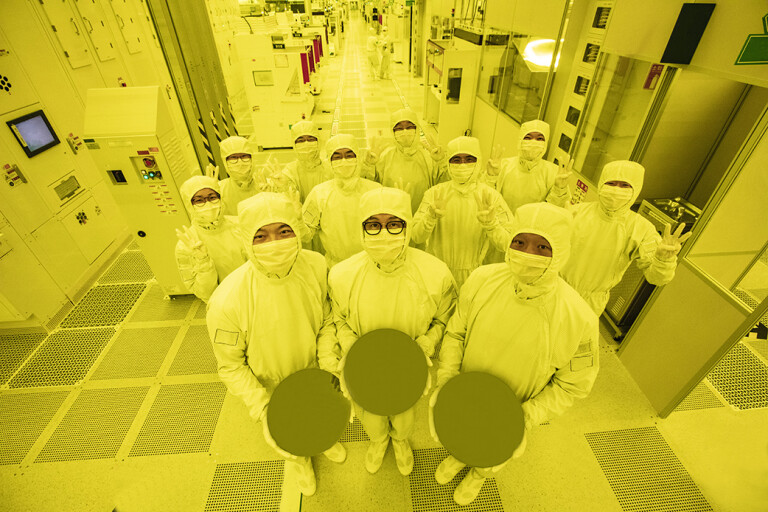

(씨넷코리아=홍상현 기자) 삼성전자가 세계 최초로GAA(Gate-All-Around) 기술을 적용한 3나노(nm, 나노미터) 파운드리 공정 기반의 초도 양산을 시작했다고 30일 밝혔다.

3나노 공정은 반도체 제조공정 가운데 가장 앞선 기술이며, 차세대 트랜지스터 구조인 GAA 신기술을적용한 3나노 공정 파운드리 서비스는 전 세계 파운드리 업체 중 삼성전자가 유일하다.

삼성전자는 3나노 공정의 고성능 컴퓨팅(HPC, High-PerformanceComputing)용 시스템 반도체를 초도 생산한데 이어, 모바일 SoC 등으로 확대해 나갈 예정이다.

삼성전자 파운드리사업부장 최시영사장은 "삼성전자는 파운드리 업계 최초로 '하이-케이 메탈 게이트(High-K Metal Gate)', 핀펫(FinFET), EUV 등 신기술을 선제적으로 도입하며 빠르게 성장해 왔고, 이번에 MBCFET GAA기술을 적용한 3나노 공정의 파운드리 서비스 또한세계 최초로 제공하게 됐다"며, "앞으로도차별화된 기술을 적극 개발하고, 공정 성숙도를 빠르게 높이는 시스템을 구축해 나가겠다"고 밝혔다.

* High-K Metal Gate: 공정이 미세화 될수록증가하는 누설전류를 효과적으로 줄일 수 있도록 절연 효과가 높은 High-K 물질을 게이트에 적용하는기술

* MBCFET: Multi-BridgeChannel Field Effect Transistor

■ 나노시트 형태의 독자적인MBCFET GAA 기술 세계 첫 적용

삼성전자는 이번에 반도체를 구성하는 트랜지스터에서 전류가 흐르는 채널(Channel) 4개면을 게이트(Gate)가 둘러 싸는 형태인 차세대 GAA 기술을 세계 최초로 적용했다.

채널의 3개면을 감싸는 기존 핀펫 구조와 비교해, GAA 기술은 게이트의면적이 넓어지며 공정 미세화에 따른 트랜지스터 성능 저하를 극복하고 데이터 처리 속도와 전력 효율을 높이는 차세대 반도체 핵심 기술로 손꼽힌다.

또한 삼성전자는 채널을 얇고 넓은 모양의 나노시트(Nanosheet) 형태로 구현한 독자적 MBCFET GAA 구조도적용했다.

나노시트의 폭을 조정하면서 채널의 크기도 다양하게 변경할 수 있으며, 기존 핀펫 구조나 일반적인 나노와이어(Nanowire) GAA 구조에비해 전류를 더 세밀하게 조절할 수 있어 고성능·저전력 반도체 설계에 큰 장점이 있다.

■ 설계 공정 기술 최적화를 통한 극대화된 PPA 구현

삼성전자는 나노시트 GAA 구조적용과 함께 3나노 설계 공정 기술 공동 최적화(DTCO,Design Technology Co-Optimization)를 통해 PPA(Power:소비전력, Performance:성능, Area:면적)를 극대화했다.

삼성전자 3나노 GAA 1세대 공정은 기존 5나노 핀펫 공정과 비교해 전력 45% 절감, 성능 23% 향상, 면적 16% 축소되었고, 이어 GAA 2세대 공정은 전력 50% 절감, 성능 30% 향상, 면적 35% 축소된다.

삼성전자는 앞으로 고객 요구에최적화된 PPA, 극대화된 전성비(단위 전력당 성능)를 제공하며, 차세대 파운드리 서비스 시장을 주도해 나갈 계획이다.

■ SAFE 파트너와 지난해부터 3나노 설계 인프라/서비스 제공

공정이 미세화되고 반도체에 더 많은 기능과 높은 성능이 담기면서, 칩의 설계와 검증에도 점점 많은 시간이 소요된다.

삼성전자는 시높시스(Synopsys),케이던스(Cadence) 등 SAFE(SamsungAdvanced Foundry Ecosystem) 파트너들과 함께 3나노 공정 기반의 반도체설계 인프라/서비스를 제공함으로써, 고객들이 빠른 시간에제품 완성도를 높일 수 있도록 시스템을 강화해 나갈 계획이다.

상카 크리슈나무티(ShankarKrishnamoorthy) 시높시스 실리콘 리얼라이제이션그룹(Silicon RealizationGroup) 총괄 매니저는 "시높시스는 삼성전자와 장기적·전략적 협력관계를 유지하고있다. 삼성전자와의 GAA기반 3나노 협력은 향후 시높시스의 디지털 디자인, 아날로그 디자인, IP 제품으로 계속 확장되어, 주요 고성능 컴퓨팅 어플리케이션을위한 차별화된 SoC를 제공할 것이다"고 말했다.

톰 베클리(Tom Beckley) 케이던스 Custom IC&PCB 그룹 부사장 겸 총괄 매니저는 "삼성전자 3나노 GAA 기반 제품 양산을 축하하며, 케이던스는 삼성전자와 협력해 자동화된 레이아웃으로 회로 설계와 시뮬레이션에서 생산성을 높일 수 있는 서비스를제공한다. 케이던스는 더 많은 테이프아웃(설계 완료) 성공을 위해 삼성전자와 협력을 계속해 나가겠다"고 말했다.